-

Notifications

You must be signed in to change notification settings - Fork 891

Improved test_insn_xN_xN semantics #132

Conversation

|

The main reason, in my opinion, to remove The latter can be applied directly at test-case level by simply copying |

There was a problem hiding this comment.

Choose a reason for hiding this comment

The reason will be displayed to describe this comment to others. Learn more.

Thanks! I learned some useful C++11 syntax along the way :-)

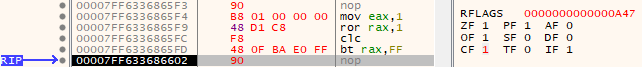

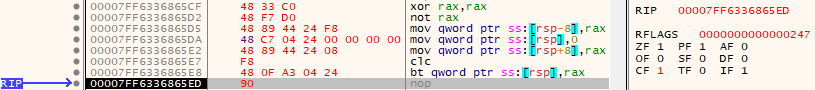

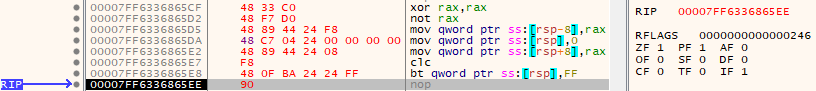

To verify this, the second operand in BT/BTC/BTR/BTS has changed from 0x7F to 0xFF, in their very last test case (this operand gets casted to -1).

I get the part where 0xFF is cast to -1, but Intel SDM doesn't seem to allow this... It only allows the Register BitOffset to be negative, when BitBase is a memory address. See Vol. 2A Table 3-2: Range of Bit Positions Specified by Bit Offset Operands, as well as Figure 3-2: Memory Bit Indexing.

eed9f7b to

e675e8a

Compare

- Removed unnecessary `readonly_dst` parameter and enforced identical destination in each test case. - Templated over integer parameters N and M representing the width of both instruction operands: test_insn_xN_xM. Unless explicitly specified, M will be equal to N by default. - Enforced sign-aware truncation of immediate types via the `imm_t` type. To verify this, the second operand in BT/BTC/BTR/BTS has changed from 0x7F to 0xFF, in their very last test case (this operand gets casted to -1). Signed-off-by: Alexandro Sanchez Bach <[email protected]>

e675e8a to

f85f447

Compare

|

All done. I've also fixed the snprintf argument indentation in the functions below test_insn_xN_xN_xN, and in test_insn_rN_rM, i.e. all remaining cases. Changes are force-pushed on top of the existing commit. Also, ignore the build issue. This is due to a Chocolatey package update, and is fixed in #133.

I've noticed it, but this seems in contradiction with Intel SDM Vol. 2A: BT—Bit Test (and BTC, BTR, BTS). Quoting below:

The section you are quoting, Intel SDM Vol. 2A: Table 3-2: Range of Bit Positions Specified by Bit Offset Operands, mentions:

Probably, rather than a contradiction what the SDM is trying to say (for BT/BTC/BTR/BTS) is that the modulo of the bit offset is taken before applying the Bit "macro", i,e, Bit(BitBase, BitOffset % Width), so the Bit "macro" always receives an operand in range 0 to [15, 31, 63]. If so, specifying 0xFF/-1 should be fine. |

|

Thanks! I agree with your interpretation of the EDIT: Oops, sorry, wrong question. |

There was a problem hiding this comment.

Choose a reason for hiding this comment

The reason will be displayed to describe this comment to others. Learn more.

I'd like to test this PR using Travis CI (since #133 has added support for running the unit tests), but I don't know how to make it retry the build... If there's no easy way, I'll just test it manually.

|

Ah, this time Travis rebuild started instantly, and finished with flying colors. |

@raphaelning You are right, the scenario The problem here is that our "fast emulator" works by converting memory-operands into register-operands, which unfortunately have a different behavior here. This seems a weird design choice of x86, but we have to comply with it. The best approach will be, I think, adding If you agree, I'll implement it that way and prepare more tests for BT/BTC/BTR/BTS. (EDIT: Fixed in #135) Also, note that this out-of-bounds behaviour does not occur on |

Removed unnecessary

readonly_dstparameter and enforced identical destination in each test case (only affects thetestinstruction so far).Templated over integer parameters N and M representing the width of both instruction operands: test_insn_xN_xM. Unless explicitly specified, M will be equal to N by default.

Enforced sign-aware truncation of immediate types via the

imm_ttype. To verify this, the second operand in BT/BTC/BTR/BTS has changed from 0x7F to 0xFF, in their very last test case (this operand gets casted to -1).Signed-off-by: Alexandro Sanchez Bach [email protected]